Preliminary Asic Scrypt (N) API & Roadmap to PoC of the Advanced Configuration Scrypt Mining Architecture on a Fpga - for ASIC Migration

Dear Miners,

We are sorry for the lack of communication. We receive many requests per day and we try to respond to all without exception. We have a 21 days of delay because we have put the part of Scrypt-N behind and it was not foreseen in the initial project.

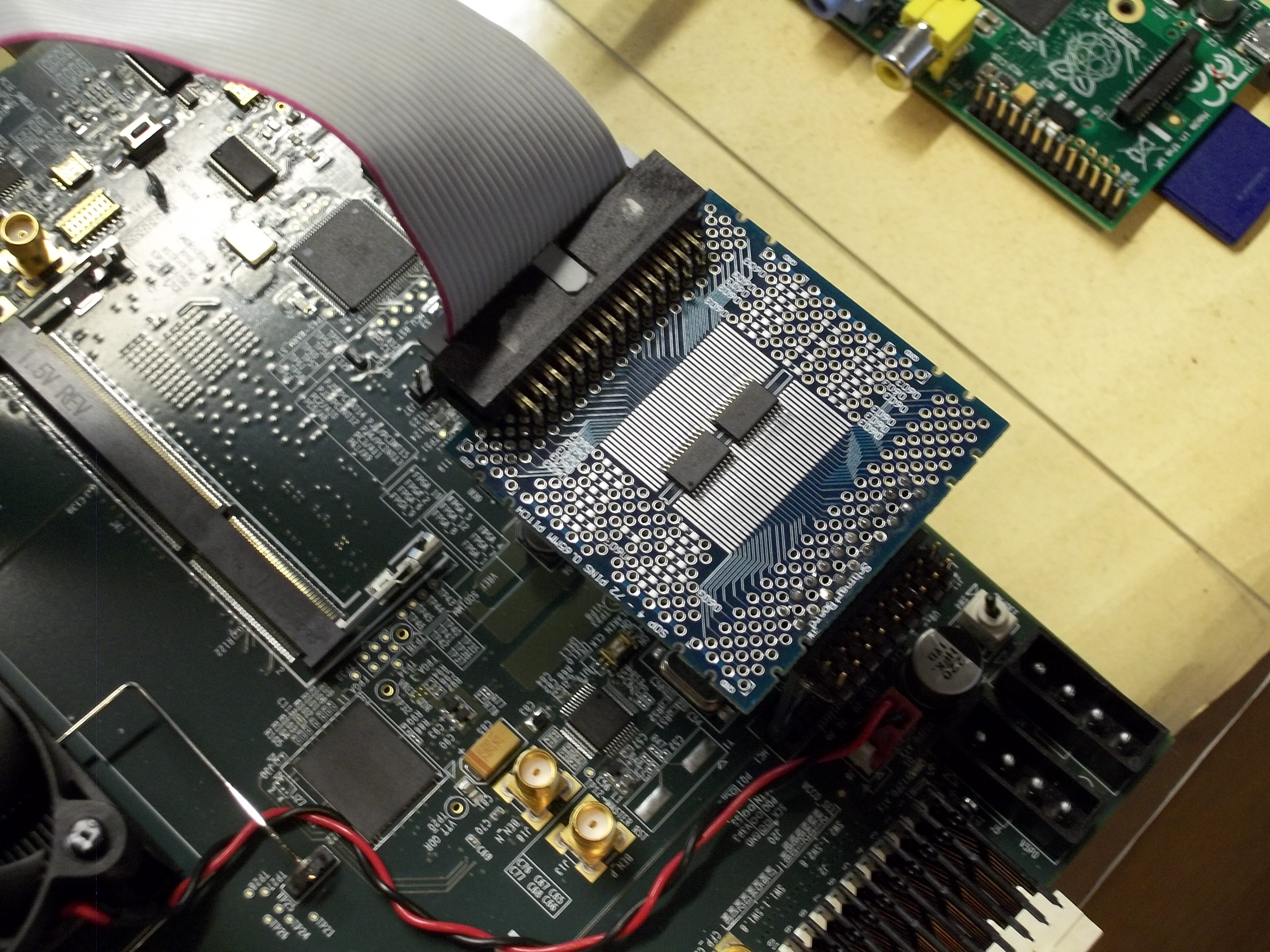

We introduced our preliminary API called the Advanced Configuration Scrypt Mining Architecture Communication API V1 (ACSMAC API V1) for the most powerful Asic scrypt(N) mining solution on the market.

The ACSMAC has been designed around a FT2232H dual port chip from FTDI and the documentation of the ACSMAC API is available on this link.

Roadmap to proof of concept of the ACSMA on a Fpga for ASIC Migration:

Below are the five phases related to the ASIC Migration:

Phase I :

- ACSMA RTL Generation using High level synthesis (done)

- Communications Interface RTL (done)

Phase II :

- ACSMA Functional Verification (done)

- Communication Interface (done)

Phase III :

- ACHRONIX FPGA implementation of short version ACSMA

- Communication interface (in progress) .

- Verification

Phase IV :

- Achronix FPGA implementation of the ACSMA full version

- Verification

Phase V :

- ACSMA ASIC restructuring of RTL code High speed buses added with signal driving circuit. Not present in the FPGA implementation.

We love Crypto

EhsMiner Team